Product Summary

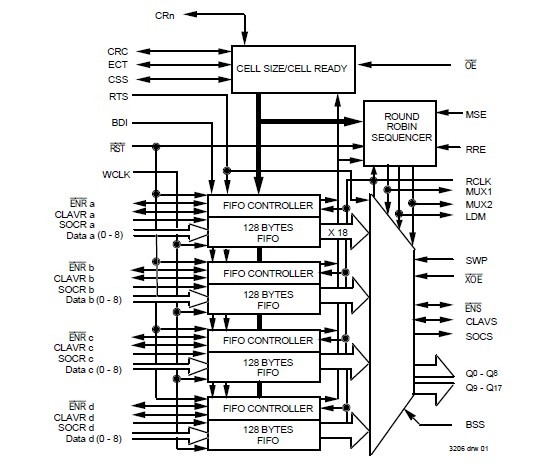

The IDT77305L12PF UtopiaFIFO is a high-speed, low power, four to one, muxed FIFO with multiple programmable modes of operation. The IDT77305L12PF can be used as a stand alone device or as a building block element. Within the UtopiaFIFO, the input FIFOs act as intermediate queues for the input streams to allow synchronization with a common output stream (see Functional Block Diagram). Each of the four input synchronous (clocked) FIFOs are 64 words (128 bytes) in depth. Separate input and output clocks are supported to 80 MHz. As a stand alone element four independent 9-bit input streams are concentrated onto one selectable 9 or 18-bit output bus. The IDT77305L12PF Bus Size Select pin (BSS) determines the desired output bus width. In a building block configuration, multiple devices can be used to multiplex larger numbers of input streams onto output buses greater than 18 bits. The principle application is in ATM networking based systems, but can be used in any data or telecommunications application requiring the merging of independent data streams into a single output.

Parametrics

IDT77305L12PF absolute maximum ratings: (1)VTERM Terminal Voltage with respect to ground: -0.5 to +7.0V; (2)TA Operating Temperature: -40 to +85℃; (3)T-Bias Temperature under Bias: -55 to +155 ℃; (4)T-STG Storage Temperature: -55 to +155 ℃; (5)IOUT DC Output Current: 50 mA.

Features

IDT77305L12PF features: (1)Four Independent Input 128 x9 FIFO Queues; (2)Nine bit wide input FIFOs; (3)Single selectable 9 or 18 bit output bus; (4)UtopiaRx or UtopiaTx Utopia compliant interface signaling options; (5)Separate clocks for input and output; (6)Selectable Automatic byte insertion for 8-bit Receive Utopia to 16-bit Receive Utopia compliance; (7)Four 155Mbs ATM input channels can be consolidated into a single 622Mbs channel with no additional glue logic; (8)Maximum through put per device over 1.4Gbps; (9)In a building block configuration multiple input channels can be multiplexed onto a 32, 64 or 128 bit bus.; (10)User programmable: byte insert/delete, UtopiaTx/UtopiaRx mode, master/slave configuration, byte swapping; (11)Selectable Round Robin Sequencer output control; (12)Data clock rates to 80 MHz; access times 8.5 ns; (13)100-pin TQPF package; (14)Separate cell ready signals for each FIFO and cell ready composite signal; (15)End of cell transfer flag.

Diagrams

|

IDT7005 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L15J |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15J8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

(China (Mainland))

(China (Mainland))